- Registrati

- Accesso

-

Carrello

(0)

Non ci sono articoli nel tuo carrello

FIRST Componens Academy | Compatibilità MIPI DSI e timing nell’integrazione dei display

Dalla News di Winstar di Marzo '26

Compatibilità MIPI DSI e meccanismi di timing nell’integrazione dei sistemi display

Nello sviluppo di prodotti display e nell’integrazione di sistemi, non è raro riscontrare errori di inizializzazione o comportamenti instabili del display, anche quando sia il SoC host sia il driver IC del display (DDIC) sono dichiarati conformi allo standard MIPI DSI.

I sintomi tipici includono schermi neri, linee di rumore verticali intermittenti o una stabilità del display incoerente tra diverse piattaforme hardware. Questi problemi sono spesso attribuiti all’hardware del pannello o alle sequenze di inizializzazione. Tuttavia, l’esperienza pratica di integrazione dimostra che la causa principale è frequentemente legata al margine di timing del D-PHY durante la transizione da LP a HS, piuttosto che a incompatibilità a livello di protocollo.

Se il comportamento del livello fisico e le condizioni al contorno del sistema non vengono valutati nelle fasi iniziali di progettazione, possono comunque verificarsi rischi di integrazione, anche quando il pannello è pienamente conforme alla specifica MIPI.

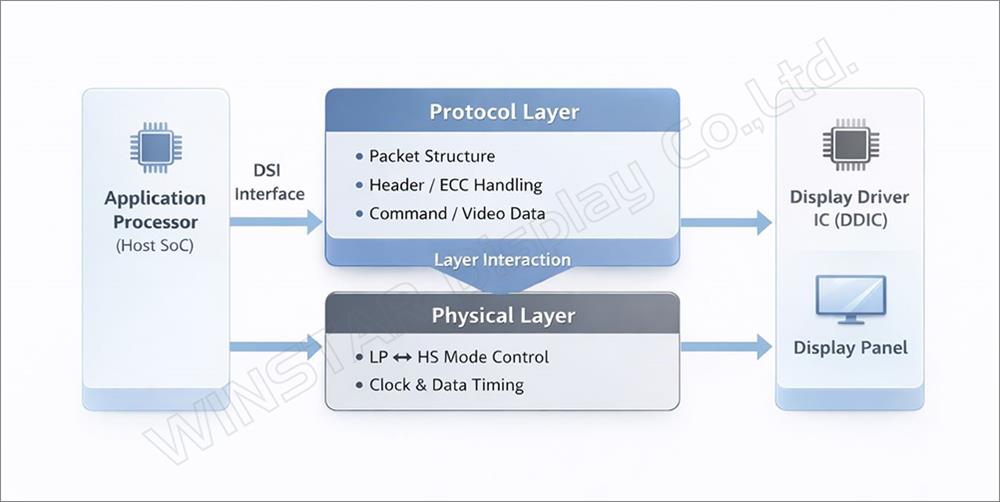

Architettura MIPI DSI e interazione tra livelli

MIPI DSI è composto da due livelli principali:

Livello Fisico (D-PHY / C-PHY)

Responsabile di:

• Trasmissione dei segnali elettrici

• Transizioni di stato delle linee

• Trasferimento dati ad alta velocità

• Controllo della finestra di timing

Livello di Protocollo

Responsabile di:

• Definizione della struttura dei pacchetti

• Header format Formato dell’header

• Protezione ECC/CRC

• Organizzazione dei dati in modalità comando e video

Nell’integrazione pratica dei sistemi, se il timing del livello fisico non rientra nella finestra di rilevamento accettabile del ricevitore, la sincronizzazione dei pacchetti e l’analisi degli header possono fallire, attivando i meccanismi di gestione degli errori a livello di protocollo.

【Figura 1】 Architettura a livello di sistema MIPI DSI e interazione tra livelli

Meccanismo di trasmissione D-PHY e sensibilità al timing

MIPI DSI utilizza una trasmissione DDR (Double Data Rate), campionando i dati sia sul fronte di salita che su quello di discesa del clock.

• La durata di un bit è definita come Unit Interval (UI)

• Un ciclo DDR equivale a 2 × UI

All’aumentare della velocità dati del D-PHY, aumenta anche la sensibilità del sistema nelle seguenti aree:

• Jitter del PLL

• Timing della transizione LP-to-HS

• Ritardo di avvio del ricevitore

• Integrità del segnale

Sebbene velocità dati più elevate migliorino le prestazioni del display, riducono anche il margine di timing disponibile.

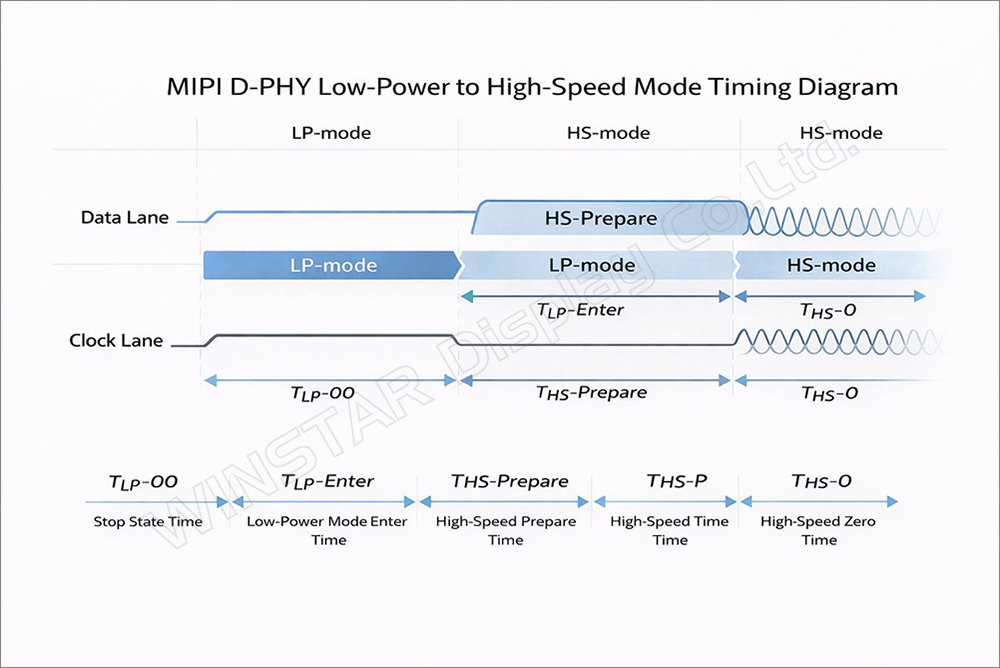

Transizione LP-to-HS e requisiti di timing

Prima di entrare in modalità High-Speed (HS), il trasmettitore deve completare la transizione LP-to-HS:

• LP-11 (Idle)

• LP-01 → LP-00

• THS-PREPARE

• THS-ZERO

• SoT (Start of Transmission)

Secondo la specifica D-PHY v1.1: THS-PREPARE + THS-ZERO > 145 ns + 10 × UI

Tuttavia, nell’integrazione reale dei sistemi display, il rispetto del limite minimo della specifica potrebbe non garantire la stabilità tra diverse piattaforme. Nella progettazione ingegneristica pratica, è generalmente necessario un margine di timing aggiuntivo per ridurre il rischio di integrazione.

【Figura 2】 Diagramma di timing della transizione LP-to-HS MIPI D-PHY

Osservazione pratica: requisiti HS-Settle oltre il minimo teorico

Durante il test di avvio (bring-up) MIPI DSI su diverse piattaforme, è stato osservato che, in alcune piattaforme SoC basate su ARM abbinate a dispositivi DDIC DSI v1.1, per un funzionamento stabile del display era necessario: THS-PREPARE + THS-ZERO > 215 ns

Questo comportamento è legato alle caratteristiche progettuali del lato ricevitore:

• Il ricevitore HS richiede tempo di stabilizzazione prima del campionamento

• I meccanismi di filtraggio interni introducono un ritardo di rilevamento

• Se la trasmissione SoT avviene troppo presto, l’avvio del ricevitore può essere incompleto

Quando il rilevamento SoT fallisce:

• Errore di allineamento dei byte

• Errori di parsing dell’header

• Mancata corrispondenza ECC

• Scarto del pacchetto

A livello di sistema, questi errori si manifestano tipicamente come schermi neri o output del display instabile.

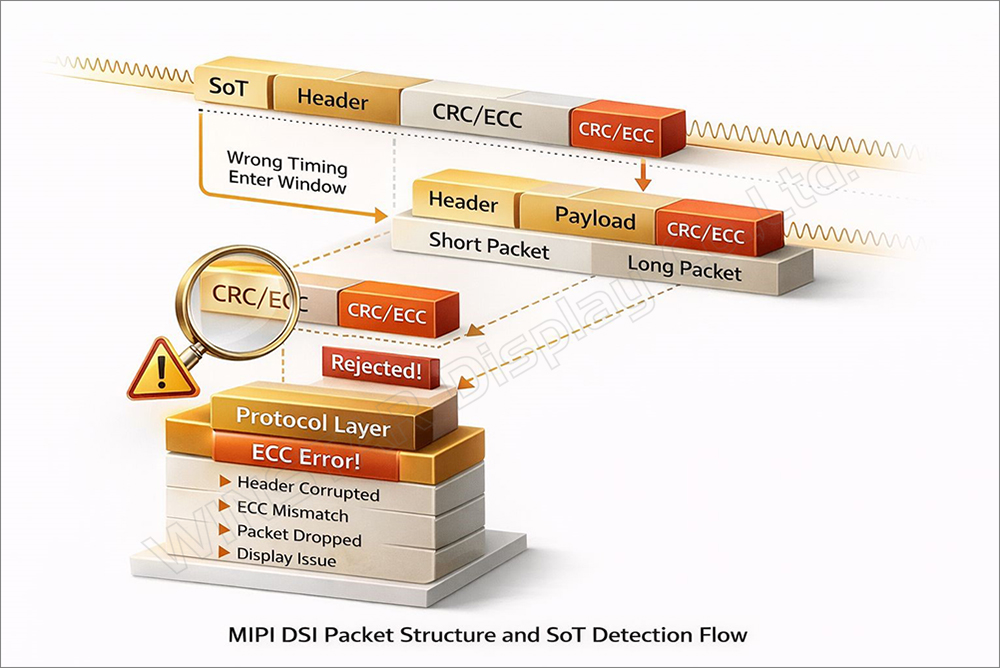

Rilevamento SoT e integrità dei pacchetti

SoT (Start of Transmission) è la sequenza di sincronizzazione che segna l’inizio dei dati ad alta velocità.

Il ricevitore deve riuscire a:

• Entrare in modalità HS

• Agganciare il timing

• Eseguire il campionamento a livello di bit nella finestra temporale corretta

Se il rilevamento SoT fallisce, possono verificarsi i seguenti problemi:

• Errori di allineamento dei byte

• Errore di decodifica dell’header

• Errori di verifica ECC

【Figura 3】 Struttura dei pacchetti MIPI DSI e flusso di rilevamento SoT

Compatibilità tra versioni DSI e differenze tra piattaforme

La corrispondenza delle versioni DSI indica solo compatibilità a livello di specifica. Non garantisce un comportamento implementativo identico.

Le diverse piattaforme SoC possono differire in:

• Architettura del PLL

• Parametri regolabili di timing di transizione

• Meccanismi di rilevamento HS-Settle del ricevitore

• Metodi di configurazione del tuning PHY

Alcune piattaforme offrono intervalli di regolazione limitati per i parametri di timing del D-PHY, il che può ridurre la flessibilità di integrazione.

Pertanto, l’integrazione del sistema display dovrebbe valutare le reali caratteristiche di implementazione della piattaforma e la capacità di tuning, piuttosto che basarsi esclusivamente sulla conformità alla versione.

Considerazioni ingegneristiche nell’integrazione dei sistemi display

La compatibilità MIPI DSI è influenzata da molteplici fattori a livello di sistema:

• Architettura PHY del SoC e caratteristiche di jitter

• Controllo dell’impedenza del PCB e integrità del segnale

• Stabilità dell’alimentazione

• EMI e condizioni ambientali di rumore

• Circuiteria di bridge IC o adattatori

Esperienza pratica WINSTAR nell’integrazione MIPI DSI

Attraverso progetti di bring-up e validazione di compatibilità MIPI DSI su diverse piattaforme, WINSTAR ha osservato che il margine di timing del livello fisico e il comportamento di rilevamento del ricevitore influenzano significativamente la stabilità complessiva del sistema.

Durante i progetti di integrazione display, WINSTAR include i seguenti step di validazione:

• Analisi del margine di transizione LP-to-HS

• Test di stabilità del rilevamento SoT

• Verifica incrociata multi-piattaforma

• Valutazione dell’integrità del segnale PCB

• Valutazione della compatibilità modulo-piattaforma

Conclusione

MIPI DSI è un’interfaccia display ad alte prestazioni. Tuttavia, la compatibilità reale non è determinata esclusivamente dalla conformità alla specifica.

La pratica ingegneristica dimostra che:

• I valori minimi di specifica rappresentano requisiti di base; un margine di timing aggiuntivo è spesso necessario per un’integrazione stabile.

• I livelli PHY e Protocol devono essere valutati congiuntamente.

• Le differenze di implementazione tra piattaforme possono influenzare il rilevamento SoT e il lock dei dati.

• L’integrazione del sistema display richiede validazione del timing cross-layer e della stabilità dei pacchetti.

Valutare il margine della transizione LP-to-HS e il comportamento di avvio del ricevitore nelle fasi iniziali dello sviluppo prodotto può ridurre significativamente i rischi di integrazione nelle fasi finali.

FAQ – Integrazione e timing MIPI DSI

D1: Perché può verificarsi uno schermo nero anche se la specifica DSI è rispettata?

Anche se la specifica è rispettata, un margine insufficiente nella transizione LP-to-HS può causare il fallimento del rilevamento SoT, portando allo scarto dei pacchetti e all’assenza di output video.

D2: La corrispondenza della versione DSI garantisce la compatibilità?

No. Differenze nell’implementazione del PHY e del ricevitore tra piattaforme possono influenzare la compatibilità reale.

D3: È sufficiente rispettare il minimo della specifica HS-Settle?

Nell’integrazione pratica multi-piattaforma, è spesso necessario un margine di timing aggiuntivo per un funzionamento stabile.

D4: Perché è necessaria una validazione cross-layer nell’integrazione dei display?

Perché la compatibilità DSI è influenzata sia dal livello fisico che da quello di protocollo; è quindi necessaria una validazione a livello di sistema per garantire prestazioni stabili.