- Registrati

- Accesso

-

Carrello

(0)

Non ci sono articoli nel tuo carrello

Conoscere le interfacce dei display: RGB 16/18/24, LVDS, parallela 6800/8080, seriale, I2C, MIPI...

Conoscere le interfacce dei display: RGB 16/18/24, LVDS, parallela 6800/8080, seriale, I2C, MIPI

Introduzione

1.Interfaccia Parallella

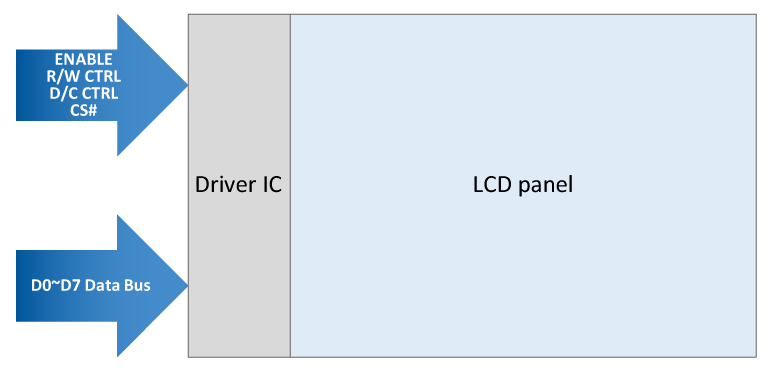

1-1 Interfaccia MCU 8080/6800

Visualizza i dati grezzi inviati tramite il bus dati in base al segnale del bus di controllo. La larghezza di banda della comunicazione dipende dall'abilitazione della velocità in esecuzione su Driver IC. LCD a matrice di punti QVGA 320x240, ovvero la larghezza di banda di comunicazione sarà 320 * 240/8 bit (larghezza dati) * 60 fps = 576 KHz al segnale ENABLE.

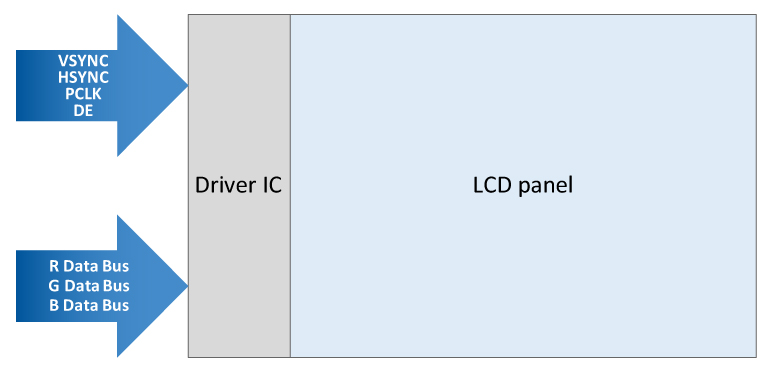

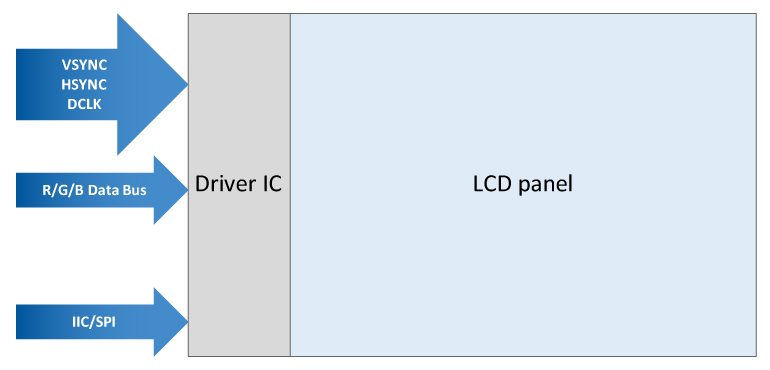

1.2 Interfaccia RGB Parallela 6/18/24 bits

L'interfaccia RGB deve trasmettere la temporizzazione dell'unità all'IC del driver del display attraverso l'ingresso/uscita dei dati in modo parallelo, inclusi dati R/G/B, segnale di sincronizzazione verticale (V-SYNC, segnale di sincronizzazione verticale), segnale di sincronizzazione orizzontale ( H-SYNC), segnale di sincronizzazione orizzontale), segnale di abilitazione dati (DE, Data Enable) e segnale di clock PCLK (Pixel Clock). L'interfaccia di visualizzazione di RGB666 è la seguente:

Visualizza i dati grezzi trasferiti come sopra. Ma la risoluzione del display sta diventando sempre più alta. ovvero WVGA 800 * 480 (pixel) * 60 fps = 23,04 MHz. (PCLC)

2.Interfaccia Seriale

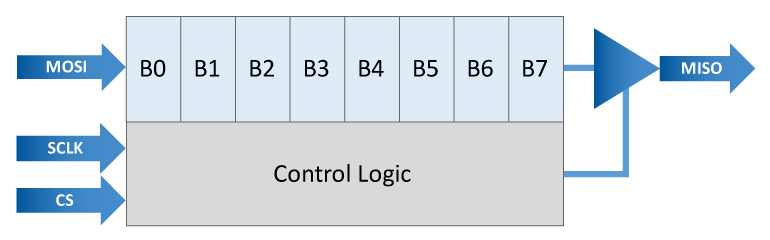

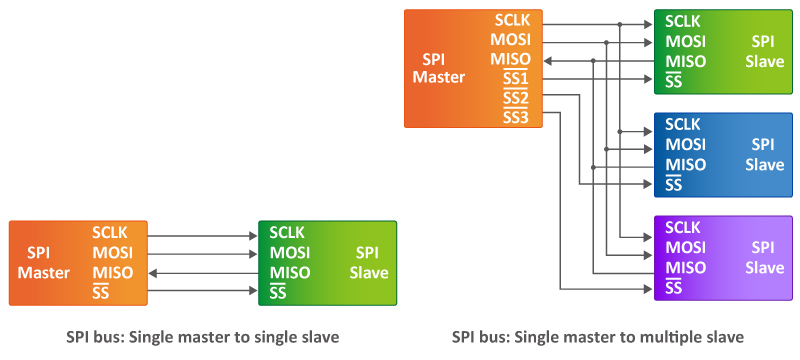

2.1 SPI (Inferfaccia Periferica Seriale)

SPI è un'interfaccia basata su master-slave, solitamente con un master (dispositivo master) e uno o più slave (dispositivi slave). Ci sono 4 pin sull'interfaccia. Il metodo di connessione e la struttura hardware sono i seguenti:

SCLK: L'orologio sincrono utilizzato da tutti i dispositivi. Il master guida questo orologio e gli slave ricevono l'orologio.

MOSI: Master out, slave in. Questa è la linea dati principale guidata dal master a tutti gli slave sul bus SPI. Solo lo slave selezionato sincronizza i dati da MOSI.

MISO: Padrone dentro, schiavo fuori. Questa è la linea dati principale guidata dallo slave selezionato al master. Solo lo slave selezionato può pilotare questo circuito. In effetti, è l'unico circuito nella disposizione del bus SPI che uno slave può mai pilotare.

CS: Selezione chip. Questo segnale è unico per ogni slave. Quando è attivo, lo slave selezionato deve guidare MISO.

Visualizza i dati trasferiti in sequenza. Larghezza di banda di comunicazione dell'interfaccia del display, ad esempio QVGA 320 * 240 (pixel) * 16 bit (profondità colore) * 30 fps = 36,864 MHz.

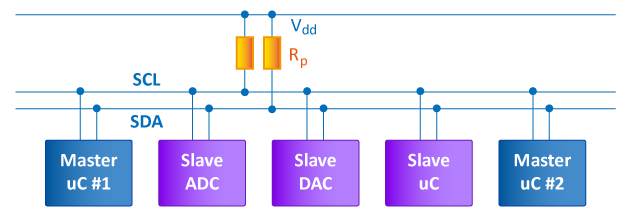

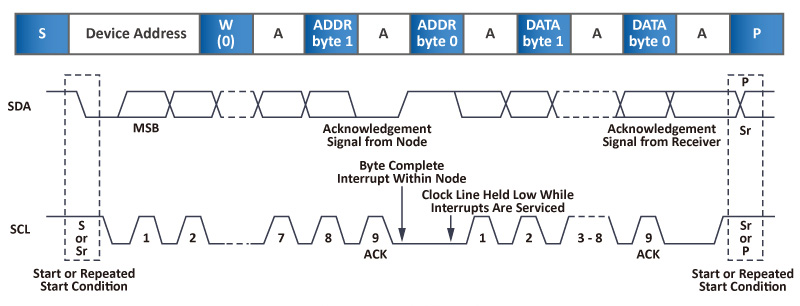

2.2 IIC (Inter-Integrated Circuit) o in alternativa noto come I²C):

Diversamente dalla base punto-punto (o punto-multipunto) di SPI, I²C è interfacciato sotto forma di un bus dati, che consente di collegare in serie più dispositivi master e più dispositivi slave. Il metodo di interfaccia e la struttura hardware sono i seguenti:

Modalità standard = 100K bit/s.

Modalità a piena velocità = 400K bit/s.

Modalità veloce = 1M bit/s.

Modalità ad alta velocità = 3,2 M bit/s.

2.3 Interfaccia Seriale RGB 6/8 bit.

Visualizza i dati trasferiti in sequenza RGB. Larghezza di banda di comunicazione dell'interfaccia del display, ad esempio QVGA 320 * 240 (pixel) * 3 punti * 30 fps = 6912000 Hz (DCLK).

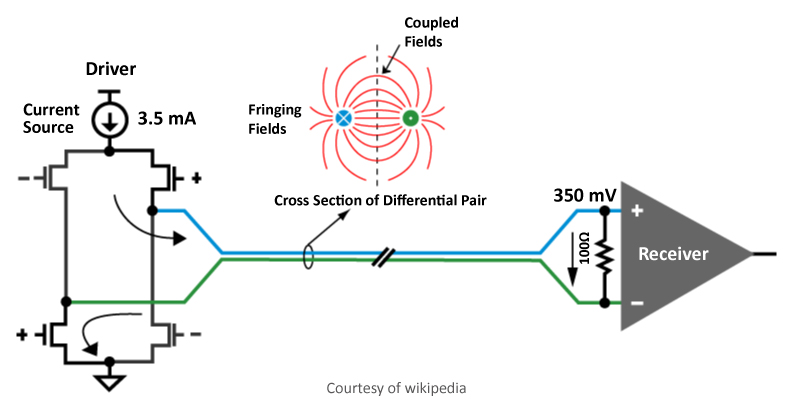

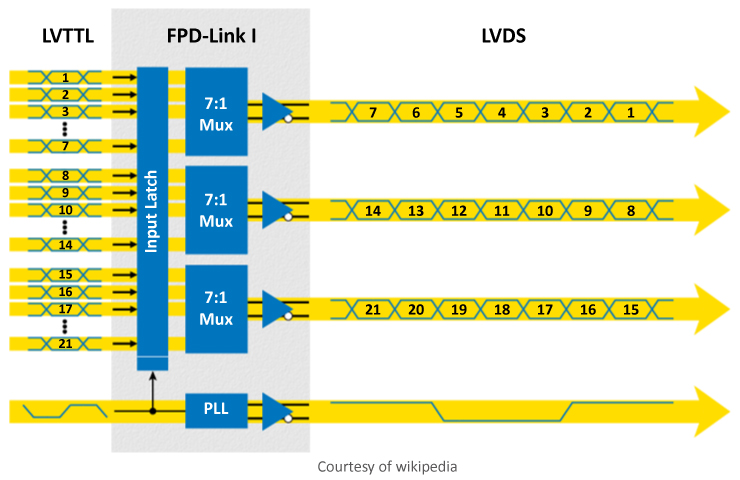

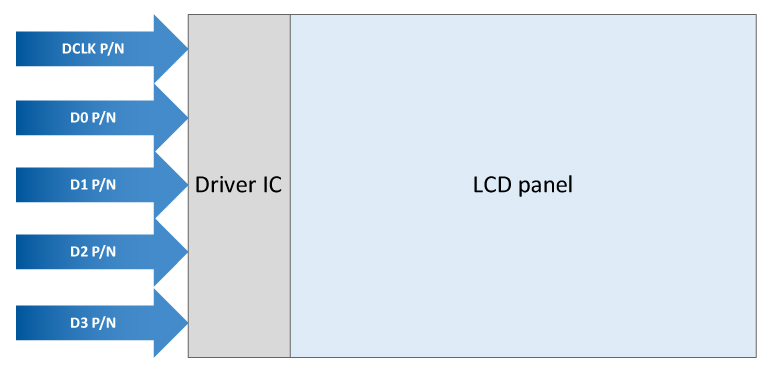

2.4 LVDS: segnale differenziale a bassa tensione. Dovrebbe nominare FPD-Link per l'interfaccia di visualizzazione.

LVDS è uno standard tecnico introdotto nel 1994 che specifica le caratteristiche elettriche di uno standard di segnalazione seriale differenziale, ma non è un protocollo. LVDS è solo una specifica del livello fisico; molti standard e applicazioni di comunicazione dati lo utilizzano e vi aggiungono sopra un livello di collegamento dati come definito nel modello OSI. LVDS funziona a bassa potenza e può funzionare a velocità molto elevate utilizzando cavi in rame a doppino intrecciato poco costosi.

All'inizio, i fornitori di computer portatili e display LCD usavano comunemente LVDS invece di FPD-Link quando si riferivano al loro protocollo. Il termine LVDS è diventato erroneamente sinonimo di Flat Panel Display Link nel vocabolario ingegneristico dei display video.

2.5 MIPI CSI/DSI: interfaccia per processore del settore mobile.

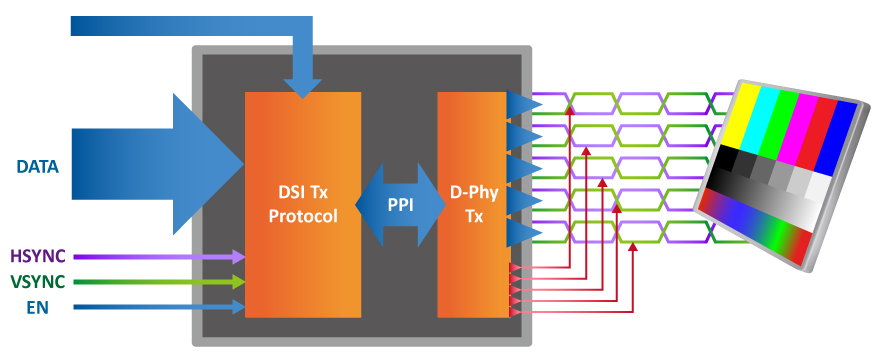

MIPI Alliance mirava a ridurre il costo dei controller di visualizzazione nei dispositivi mobili. Definisce un bus seriale e un protocollo di comunicazione tra l'host, l'origine dei dati dell'immagine e il dispositivo di destinazione. È l'obiettivo previsto per LCD e tecnologie di visualizzazione simili.

DSI specifica un bus seriale point-to-point di segnalazione differenziale ad alta velocità (ad es. 4,5 Gbit/s/lane per D-PHY 2.0). Questo bus include una corsia di clock ad alta velocità e una o più corsie di dati.

I dati dell'immagine sul bus sono interlacciati con segnali di intervalli di soppressione orizzontali e verticali. I dati vengono trasferiti al display in tempo reale e non memorizzati dal dispositivo per salvare la memoria frame buffer nel display. Tuttavia, significa anche che il dispositivo deve essere continuamente aggiornato (a una velocità come 30 o 60 fotogrammi al secondo) o perdere l'immagine. I dati immagine vengono inviati solo in modalità HS. In modalità HS, i comandi vengono trasmessi durante l'intervallo di blanking verticale.

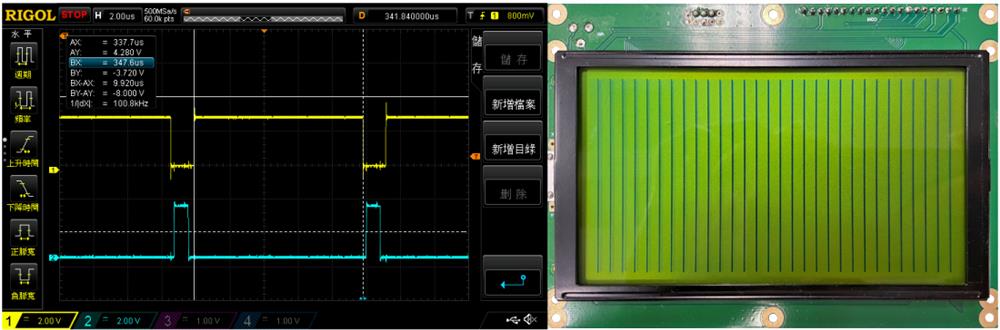

Un esempio sperimentale di interfaccia display MCU 8080/6800:

Un controller LCD è stato gradualmente eliminato e il cliente vorrebbe avere un modulo compatibile pin-to-pin per sostituirlo. I proprietari di RD avevano progettato un PCB con un MCU per l'interfaccia compatibile. I risultati sperimentali sul segnale ENABLE devono essere lunghi almeno 9.92uS. Ciò significa che il massimo BW di comunicazione è di circa 100 KBPS.

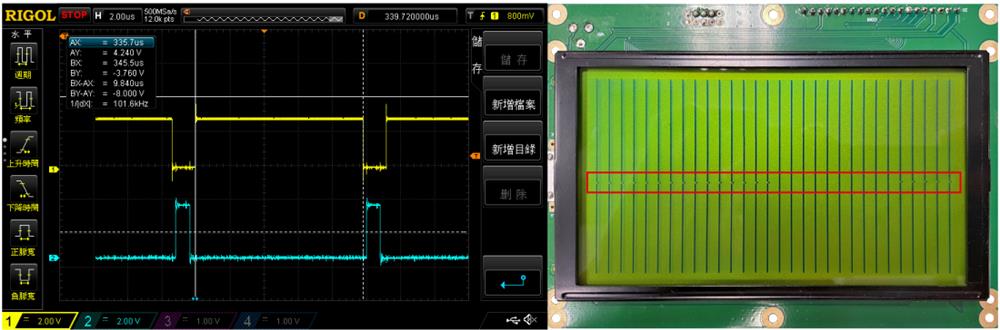

Possiamo vedere alcuni punti difettosi di seguito quando si accorcia il tempo ENABLE a 9,84 uS (la velocità di comunicazione è fino a 101 KBPS).

Una tabella di confronto sull'interfaccia del display:

Quale interfaccia è la migliore? Non esiste una risposta assoluta a questa domanda. Gli utenti dovrebbero scegliere l'interfaccia adatta per le loro applicazioni, non la migliore. Vediamo il seguente confronto dei pro e dei contro di queste interfacce.

| Display Interface | Resolution | Speed | Pin Count. | Noise | Power Consumption | Connect Distance | Cost |

|---|---|---|---|---|---|---|---|

| MCU 8080/6800 | Middle | Low | More | Middle | Low | Short | Low |

| RGB 16/18/24 | Middle | Fast | More | Worst | High | Short | Low |

| SPI | Small | Low | Less | Middle | Low | Short | Low |

| I²C | Small | Low | Less | Middle | Low | Short | Low |

| Serial RGB 6/8 | Middle | Fast | Less | Worst | High | Short | Low |

| LVDS | Large | Fast | Less | Best | Low | Long | High |

| MIPI | Large | Fastest | Less | Best | Low | Short | Average |